1. a) Present the binary number representing the decimal number -22 as an 8-bit two's complement binary number. Please explain!

**b**) if the 6-bit binary number 100111 is said to be in signed magnitude format, what is the absolute value of that binary number as a decimal number? Please explain!

c) if the hexadecimal number 96 is said to represent an 8-bit two's complement binary number, what is the absolute value of that binary number as a decimal number. Please explain!

**d**) how many bits are needed to present the decimal number from 0 to 999 as binary coded decimal numbers (BCD)? Please explain!

e) how binary numbers and digital logic are related to each other?

f) how many different truth tables can be presented with three logic variables? Please explain!

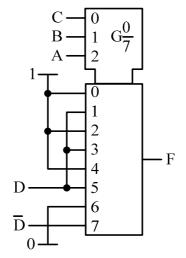

2. Analyse the following digital logic. One of the variables (D) of the logic function F(A,B,C,D) is connected to some of the data inputs of the 8:1 multiplexer (MUX), and the rest of the variables are connected to the select inputs of the MUX. Present:

**a**) the logic function of F representing the logic diagram without any minimisation

**b**) Karnaugh map of F

c) logic function of F as minimised product of sums

d) logic function of F as minimised sum of products

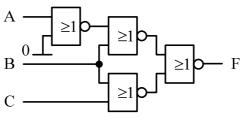

3. Analyse the following NOR-logic. One input is connected to a logic zero. Present:

a) identically behaving logic using only 2-input NAND-gates

**b**) Karnaugh map of F

c) logic function of F as minimised product of sums

© 2010 Antti Mäntyniemi

4. How would you realise the following operations related to synchronous logic? Assume that all flip-flops are clocked continuously with a common clock signal. You can draw a picture and explain in writing.

a) the content of a D-flip-flop must be zeroed synchronously with a certain clock edge, otherwise the next state of the D-flip-flop is determined by the next state decoding logic

**b**) a new value must be synchronously loaded to a D-flip-flop with a certain clock edge, otherwise the state of the D-flip-flop remains the same

c) an asynchronous input signal must be reliably synchronised to the clock signal so, that a pulse with a width of one clock cycle is generated each time the input signal changes its state

d) what is the difference between combinational logic and sequential logic (state machines)?

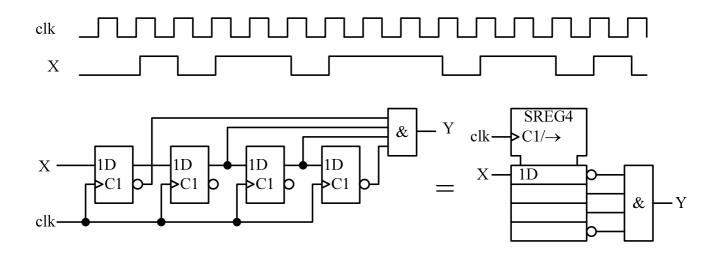

Analyse the operation of the following logic. Input signal X is synchronous with respect to the 5. clock signal.

a) fill in the timing diagram by adding to the waveforms the outputs of all flip-flops and the output signal Y

b) to what characteristics of a D-flip-flop is the operation of the logic based on? Note: all flip-flops receive the clock signal at the same time.

c) fill in the sentence describing the behaviour of the logic:

"The logic recognises \_\_\_\_\_\_ logic ones in the input signal X"